## **Contents**

## **Chapter 1: Frame Overview**

| 1.1 | Introduction1-2   |                                           |  |

|-----|-------------------|-------------------------------------------|--|

| 1.2 | Specifications1-3 |                                           |  |

| 1.3 | 1.3 Installation  |                                           |  |

|     | 1.3.1             | Mounting Requirements 1-8                 |  |

|     | 1.3.2             | Cooling Requirements 1-8                  |  |

|     | 1.3.3             | Power Supply1-8                           |  |

|     | 1.3.4             | Internal Battery Supply1-8                |  |

|     | 1.3.5             | External Battery Supply1-9                |  |

|     | 1.3.6             | 5300ET Electronic Timer Configuration1-9  |  |

|     | 1.3.7             | Rear Panel Connections 1-10               |  |

|     | 1.3.8             | Calibration 1-14                          |  |

| 1.4 | Opera             | tion 1-15                                 |  |

|     | 1.4.1             | Front Panel Control                       |  |

|     | 1.4.2             | RS232 and Telephone Line Control 1-19     |  |

| 1.5 | Opera             | tion Summary 1-30                         |  |

|     | 1.5.1             | Front Panel1-30                           |  |

|     | 1.5.2             | RS232 And Telephone Line Control          |  |

| 1.6 | Config            | guration of the Time and Control Code1-33 |  |

|     | 1.6.1             | SMPTE Serial Time Code1-33                |  |

|     | 1.6.2             | Composition of the Time Address           |  |

|     | 1.6.3             | Auxiliary Offset                          |  |

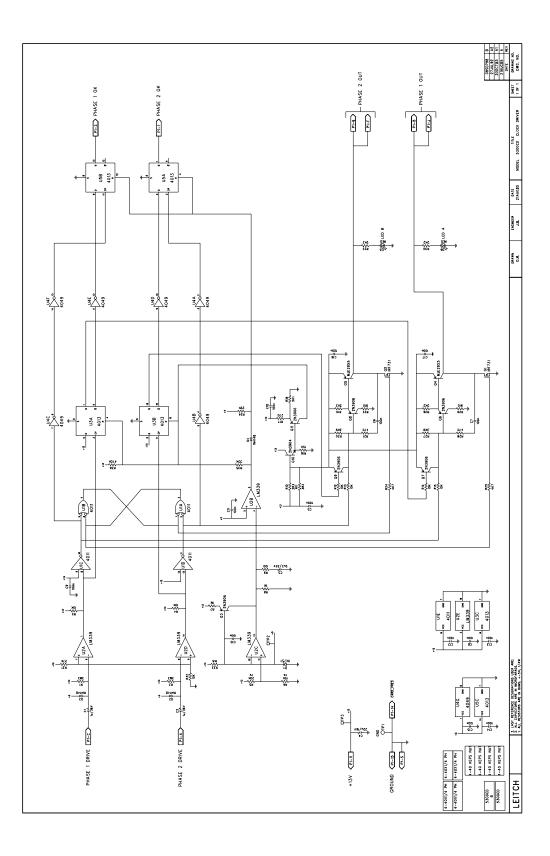

| 1.7 | CSD-:             | 5300N System Schematic 1-36               |  |

| Cha | pter 2            | 2: 5300BH Batter Holder                   |  |

| 2.1 | Circui            | t Description2-3                          |  |

| 2.2 | 5300E             | BH Battery Holder Schematic               |  |

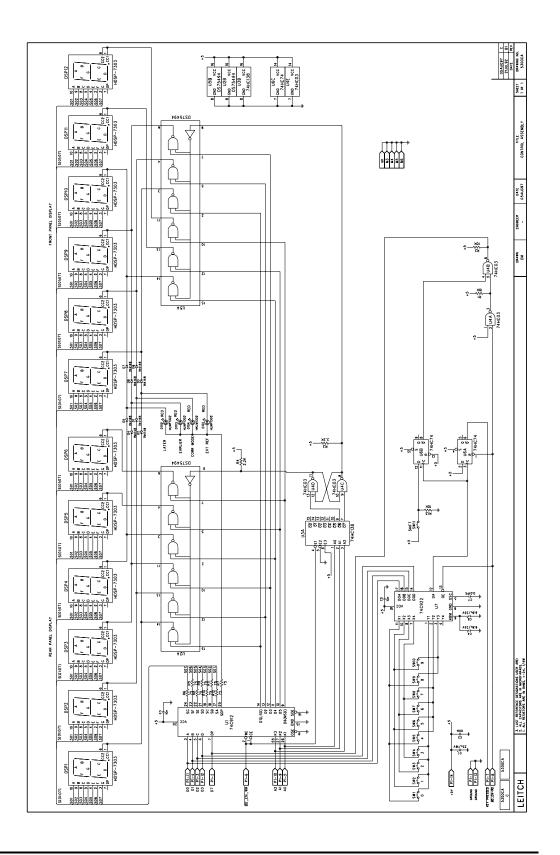

| Cha | pter 3            | 3: 5300CA Control Assembly Module         |  |

| 3.1 | Circui            | t Description                             |  |

|     | 3.1.1             | Processor Interface                       |  |

|     | 3.1.2             | Display Circuitry                         |  |

|     | 3.1.3             | The Keyboard Encoder                      |  |

| 3.2 | 53000             | CA Control Assembly Schematic             |  |

|     |                   |                                           |  |

## **Chapter 4: 5300ET Electronic Timer Module**

| 4.1 | Circui                        | it Description <sup>2</sup>           | 4-3 |  |

|-----|-------------------------------|---------------------------------------|-----|--|

|     | 4.1.1                         | System Clock                          | 4-3 |  |

|     | 4.1.2                         | Memory Map                            | 4-3 |  |

|     | 4.1.3                         | Synchronous Processor                 | 4-4 |  |

|     | 4.1.4                         | Serial Time Data/Clock                | 4-5 |  |

|     | 4.1.5                         | Parallel BCD Time Data                | 4-5 |  |

|     | 4.1.6                         | 1 Hz and 60 Hz/50 Hz Logic Levels     | 4-6 |  |

|     | 4.1.7                         | Time Code Output <sup>2</sup>         | 4-6 |  |

|     | 4.1.8                         | Aural Time Markers                    | 4-6 |  |

|     | 4.1.9                         | Impulse Clock Drive                   | 4-7 |  |

|     | 4.1.10                        | ) Ring Detection Circuit <sup>2</sup> | 4-7 |  |

|     | 4.1.11                        | Watch Dog and Reset Circuit           | 4-8 |  |

|     | 4.1.12                        | 2 Interprocessor Communication        | 4-9 |  |

|     | 4.1.13                        | 3 Asynchronous Processor              | -10 |  |

|     | 4.1.14                        | 4 Display Control                     | -10 |  |

|     | 4.1.15                        | 5 Keyboard Control 4-                 | -11 |  |

|     | 4.1.16                        | 5 Keyboard Beep 4-                    | -11 |  |

|     | 4.1.17                        | 7 Non-Volatile EEPROM 4-              | -11 |  |

|     | 4.1.18                        | 8 Modem Interface                     | -12 |  |

|     | 4.1.19                        | 9 RS232 Interface                     | -12 |  |

|     | 4.1.20                        | ) External Reference                  | -13 |  |

|     | 4.1.21                        | Power Supply4-                        | -13 |  |

| 4.2 | 5300E                         | ET Electronic Timer Schematic 4-      | -13 |  |

| Cha | pter !                        | 5: 5300 Master Oscillator Module      |     |  |

| 5.1 | Circui                        | it Description                        | 5-3 |  |

|     | 5.1.1                         | Crystal Oscillator                    | 5-3 |  |

|     | 5.1.2                         | Main Clock Reference                  | 5-3 |  |

|     | 5.1.3                         | System Clock                          | 5-3 |  |

|     | 5.1.4                         | 5 MHz Reference Output Signal         | 5-4 |  |

|     | 5.1.5                         | 100 kHz/1 MHz Reference Output        | 5-4 |  |

|     | 5.1.6                         | External Reference                    | 5-4 |  |

| 5.2 | Oscill                        | lator Calibration Procedure           | 5-5 |  |

| 5.3 | 5300N                         | MO Master Oscillator Schematic5       | 5-5 |  |

| Cha | Chapter 6: 5300MB Modem Board |                                       |     |  |

| 6.1 | -                             | it Description                        | 5-3 |  |

|     |                               | Line Interface                        |     |  |

|     |                               |                                       |     |  |

|      | 6.1.2  | Ring Detection Circuit                         | 6-3 |

|------|--------|------------------------------------------------|-----|

|      | 6.1.3  | Hybrid Circuit                                 |     |

|      | 6.1.4  | Modem Circuit                                  |     |

|      | 6.1.5  | Dialing                                        | 6-5 |

|      | 6.1.6  | Pulse                                          |     |

|      | 6.1.7  | Audio Output                                   |     |

| 6.2  | 5300N  | MB Modem Board Schematic                       | 6-6 |

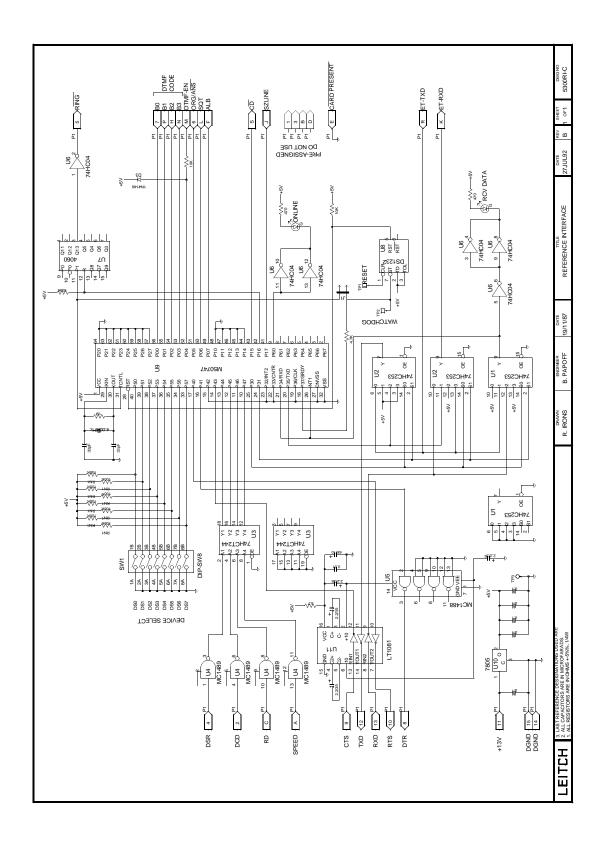

| Cha  | pter ' | 7: 5300 RI Reference Interface Module          |     |

| 7.1  | Introd | luction                                        |     |

|      | 7.1.1  | Connections                                    |     |

|      | 7.1.2  | DIP Switch Settings                            | 7-6 |

| 7.2  | Trimb  | ble Navigation Acutime GPS Smart Rodal Antenna | 7-6 |

|      | 7.2.1  | Installation                                   | 7-6 |

|      | 7.2.2  | CSD-5300 Configuration                         | 7-6 |

|      | 7.2.3  | Internal Call Sequence                         | 7-7 |

|      | 7.2.4  | General Description                            |     |

|      | 7.2.5  | Computer Interface — RS-232                    |     |

|      | 7.2.6  | Dimensions:                                    |     |

|      | 7.2.7  | System Component Description                   |     |

|      | 7.2.8  | Mechanical Interface - Antenna Mounting        |     |

|      | 7.2.9  | Electrical Interface                           |     |

| 7.3  | Hayes  | s Smartmodems                                  |     |

| 7.4  | Impor  | tant Notes for Usage with all Radio Receivers  |     |

| 7.5  | Instal | lation Procedures For The Supported Receivers: |     |

|      | 7.5.1  | Precision Standard Time Inc. Receiver          |     |

|      | 7.5.2  | Kinemetrics Radio Receivers                    |     |

|      | 7.5.3  | European Electronic Systems - ESS Model M201   |     |

|      | 7.5.4  | Radio Code Clocks Radio Receivers -RCC8000     |     |

| 7.6  | Circui | it Description                                 |     |

| 7.7  | 5300E  | ET Interface                                   |     |

| 7.8  | Mode   | m/Radio Receiver Interface                     |     |

| 7.9  | Opera  | tion                                           |     |

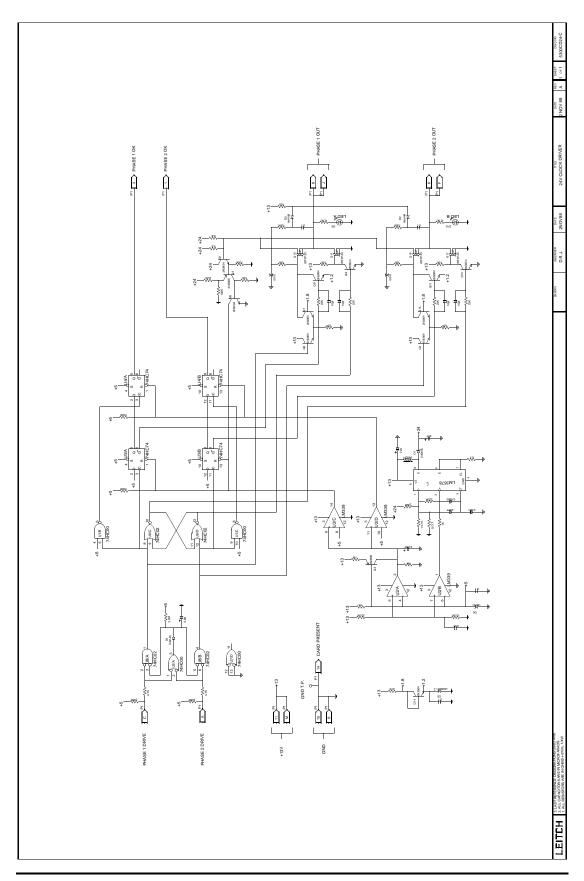

| 7.10 | 5300F  | RI Schematic                                   |     |

| Cha  | pter   | 8: 5300CD Clock Driver Module                  |     |

| 8.1  | -      | it Description                                 |     |

|      |        | Clock Drive                                    |     |

|      | 8.1.3  | Overcurrent Protection           |      |

|------|--------|----------------------------------|------|

|      | 8.1.4  | Power Failure Detector           |      |

| 8.2  | 53000  | CD Clock Driver Schematic        |      |

| Cha  | pter 9 | 9: 5300CD-24 Clock Driver Module |      |

| 9.1  | Circui | it Description                   |      |

|      | 9.1.1  | Clock Drive                      |      |

|      | 9.1.2  | Status Report                    |      |

|      |        | Overcurrent Protection           |      |

|      | 9.1.4  | Power Failure Detector           |      |

|      | 9.1.5  | 24V Switching Regulator          |      |

| 9.2  | 53000  | CD-24 Schematic                  |      |

| Cha  | pter 1 | 10: 5300PS Power Supply          |      |

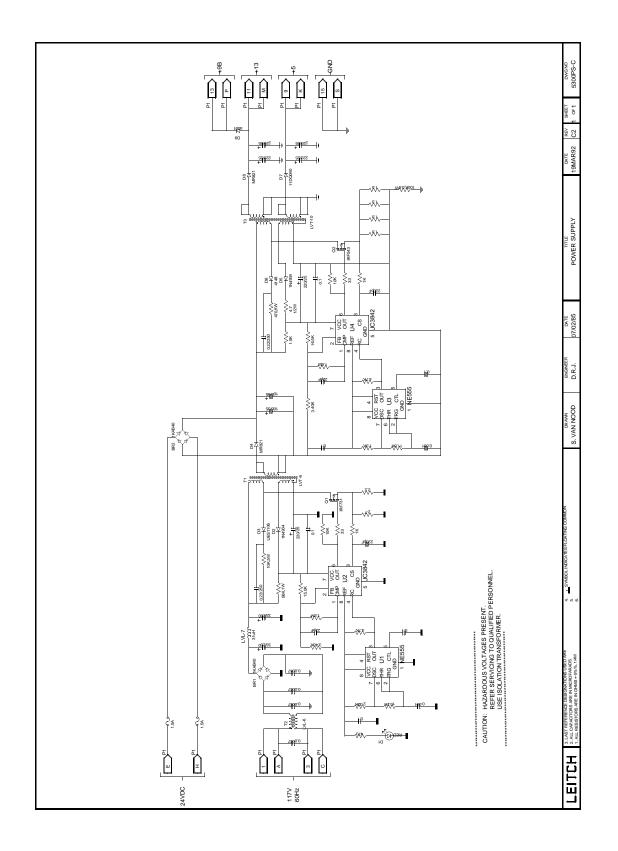

| 10.1 | Circui | it Description                   | 10-3 |

|      | 10.1.1 | Primary Power Converter          | 10-3 |

|      | 10.1.2 | 2 Secondary Power Converter      | 10-4 |

| 10.2 | 5300P  | PS Power Supply Schematic        | 10-5 |

# Chapter 1

## Frame Overview

| 1.1 | Introduction1-3   |                                           |  |

|-----|-------------------|-------------------------------------------|--|

| 1.2 | Specifications    |                                           |  |

| 1.3 | Instal            | lation                                    |  |

|     | 1.3.1             | Mounting Requirements 1-8                 |  |

|     | 1.3.2             | Cooling Requirements                      |  |

|     | 1.3.3             | Power Supply1-8                           |  |

|     | 1.3.4             | Internal Battery Supply 1-8               |  |

|     | 1.3.5             | External Battery Supply                   |  |

|     | 1.3.6             | 5300ET Electronic Timer Configuration1-9  |  |

|     | 1.3.7             | Rear Panel Connections                    |  |

|     | 1.3.8             | Calibration 1-14                          |  |

| 1.4 | Opera             | tion 1-15                                 |  |

|     | 1.4.1             | Front Panel Control 1-15                  |  |

|     | 1.4.2             | RS232 and Telephone Line Control 1-19     |  |

| 1.5 | Operation Summary |                                           |  |

|     | 1.5.1             | Front Panel1-30                           |  |

|     | 1.5.2             | RS232 And Telephone Line Control 1-31     |  |

| 1.6 | Confi             | guration of the Time and Control Code1-33 |  |

|     | 1.6.1             | SMPTE Serial Time Code1-33                |  |

|     | 1.6.2             | Composition of the Time Address 1-35      |  |

|     | 1.6.3             | Auxiliary Offset 1-35                     |  |

| 1.7 | CSD-              | 5300N System Schematic 1-36               |  |

## **1.1 Introduction**

The CSD-5300 Clock System Driver is designed to be a central source of time for broadcast or computer facilities. It operates as a high stability stand alone clock. If required, it will automatically update its time from a central standard. The CSD-5300 unit provides the following outputs:

- 3. SMPTE/EBU Serial Time Code,  $600 \Omega$  bal.

- 4. SMPTE/EBU Serial Time Code, Low Z bal.

- 5. Serial BCD Time

- 6. 1 Hz

- 7. 60/50 Hz

- 8. 2-phase, 12/24 VDC Impulse Drive

- 9. Parallel BCD Time

- 10. 1 MHz / 100 kHz (jumper selectable)

- 11. 5 MHz Sine Wave, 75  $\Omega$ , 2 Vp-p

- 12. Time Markers, 600  $\Omega$  bal.

- 13. Time Markers Present

- 14. Time and Date, ASCII 300 baud, Bell 103 Modem (on demand)

- 15. Time and Date, ASCII RS232 300 baud (on demand)

## 1.2 Specifications

#### Inputs

| External Reference |                                             |

|--------------------|---------------------------------------------|

| Frequency          | 5 or 10 MHz                                 |

| Level              | 2 Vp-p ±3 dB                                |

| Impedance          | 75 Ohms, loop-through                       |

| External Strobe    |                                             |

| Input              | contact closure or logic level falling edge |

| Logic levels       | TTL compatible                              |

#### Outputs

#### **SMPTE /EBU Time Code**

SMPTE/EBU (nondrop frame) Format Output 1 Level +10 dBm nominal unloaded, -3 dB into 180 Ohms Impedance Low-Z, balanced Output 2 Level +4 dBm nominal Impedance 600 Ohms, balanced **RS232** Interface Interface type data set Baud rate 300 Parity none Data format 8 bits, 1 stop bit **BCD** Parallel Time Data format BCD parallel frame count, seconds, minutes and hours Level 5 volt logic levels Drive capability 4000 Series, CMOS outputs. **BCD Serial Time** Data format BCD serial frame count, seconds, minutes and hour with related clock and latch pulses Clock format data valid on falling edge of clocks **BCD Serial Time (Cont.)** Latch format active low pulse at end of frame Level 5 volt logic levels HC CMOS outputs (LSTTL compatible) Drive capability **Marker Beeps** 1200 Hz (1000Hz for EBU) Frequency Duration 0.3 second Timing 1 pulse on the hour, double pulse on the half hour with 0.3 sec. spacing. Separate enable for each signal.

Level

Impedance

8 dBm nominal

600 Ohms balanced

#### **Tone Present**

Output Level Drive capability

#### **Reference Outputs**

Output 1 Frequency Level Impedance Output 2 Frequency

Level

Drive capability

## 1Hz, 60Hz/50Hz

Frequencies Level

Drive capability

#### **Time Valid**

Output

Level

Drive capability

**Telephone Interface** Format

Modem

Dialing capability

Receive sensitivity Transmit level Connector High during tone output +5 V logic levels HC CMOS output (LSTTL compatible)

5 MHz 2 Vp-p 75 Ohms 100 kHz / 1 MHz square wave (jumper selectable) 5 volt logic levels HCCMOS output (LSTTL compatible)

1Hz, 60Hz/50Hz square waves5 volt logic levelsHC CMOS output (LSTTL compatible)

active high 5 V logic levels HC CMOS output (LSTTL compatible)

Bell 103 compatible, originate and answer modes autoanswer, autodial

with speaker and volume control

up to 25 digits, DTMF, pulse or combination with programmable interdigit delay.

-50 dBm

-10 dBm

modular jack, compatible with RJ11, RJ12 and RJ13 type jacks

| Impulse Drive                                                             |                                                         |

|---------------------------------------------------------------------------|---------------------------------------------------------|

| System                                                                    | 2-phase, +12/24 VDC                                     |

| Maximum load                                                              | 25 impulse clocks                                       |

| Drive protection                                                          | current limiting                                        |

| Clock correction after power failure or shorted outputs                   | automatic                                               |

| Performance                                                               |                                                         |

| Oscillator aging                                                          | <5 parts in 108 per month                               |

| Oscillator stability with 10% line voltage variation                      | <1 part in 108                                          |

| Oscillator stability with temperature change from 0° to 50°C              | <1 part in 108                                          |

| Oven warm up time                                                         | <20 minutes                                             |

| Time acquisition accuracy<br>Over telephone line<br>Using external strobe | <1 ms of source *<br><20 µs of strobe                   |

| Compensation for telephone line loop delay                                | automatic                                               |

| Detection of asymmetric loop                                              | automatic with user definable parameters                |

| External standby battery capability                                       | unit fully operational                                  |

| Internal standby battery capability                                       | timekeeping only for over 8 hours (no outputs enabled). |

\* Under normal telephone line operating conditions. Operation in extraordinary conditions cannot be guaranteed.

## **Temperature Range**

| Operating                        | 0-50°C     |

|----------------------------------|------------|

| Performance                      | 5-40°C     |

| Electrical                       |            |

| Line Voltage                     | 95/135 VAC |

| Frequency                        | 60 Hz/50Hz |

| Power Consumption                | 20 VA      |

| External standby battery Voltage | 20-26 V    |

| Power Consumption                | 15 W       |

| Mechanical                                                       |                      |  |  |

|------------------------------------------------------------------|----------------------|--|--|

| Height                                                           | 44 mm (1.75 inches)  |  |  |

| Width                                                            | 483 mm (19 inches)   |  |  |

| Depth from mounting surface                                      | 290 mm (11.5 inches) |  |  |

| Overall depth                                                    | 320 mm (12.5 inches) |  |  |

| Weight                                                           | 5.7 kg (12.5 lbs.)   |  |  |

| Specifications and designs are subject to change without notice. |                      |  |  |

## **1.3 Installation**

The CSD-5300 Clock System Driver is carefully inspected, tested and calibrated before shipment to ensure stable and trouble-free service. Please check the unit for any visible damage which may have been caused during transit. Ensure that the modules have remained properly seated in the mounting frame.

## **1.3.1** Mounting Requirements

The CSD-5300 unit requires 44 mm (1.75 inches) of standard 483 mm (19 inches) rack space. The minimum depth required behind the mounting surface is 290 mm (11.5 inches).

## **1.3.2** Cooling Requirements

The Clock System Driver is designed to meet specifications in an ambient temperature range of  $5^{\circ}$ C to  $40^{\circ}$ C. No special provisions for cooling are necessary, but care should be taken to prevent excessive heat rise in closed, unventilated equipment racks.

## **1.3.3** Power Supply

The power consumption of the CSD-5300 unit is 20 VA based on the normal module complement at nominally 95/135 VAC, 60 Hz/50 Hz. The driver is equipped with a detachable power cord and a resettable circuit breaker.

## **1.3.4 Internal Battery Supply**

The CSD-5300 unit is equipped with an internal battery pack. In case of a power failure, only the time keeping circuitry is kept operational and all outputs are disabled.

The battery pack contains three 9 Volt batteries. If primary batteries are used, type MN1604 alkaline batteries or equivalent, are recommended. With this type of battery, the circuitry will operate for over 8 hours.

If secondary batteries are to be used, resistors can be added to the battery pack to allow charging.

## **NOTE:** To prevent discharging of the internal battery supply, the battery pack is removed for shipment.

## 1.3.5 External Battery Supply

Provision is made to allow the connection of an external, user supplied, 24 Volt battery if operation of the entire unit is required during AC power failures. The connecting terminal block for the external battery is located on the rear panel.

## **1.3.6 5300ET Electronic Timer Configuration**

The DIP switch on the front of the 5300ET module is used to configure many of the operational parameters of the CSD-5300 unit. All switches enable their corresponding function when in the up position. The DIP switch is connected as follows:

#### Switch

| 1 | Input HMS offset / AUX offset       |

|---|-------------------------------------|

| 2 | Keyboard beep enable                |

| 3 | Telephone system mode access enable |

| 4 | Telephone answer enable             |

| 5 | Half hour tone enable               |

| 6 | Hour tone enable                    |

| 7 | Impulse clock driver enable         |

| 8 | Auto Change/Normal Mode Selection   |

|   |                                     |

For further details on the functions, please refer to the operation section of this manual.

## **1.3.7** Rear Panel Connections

## **Telephone Line**

The telephone line connector is a standard 6-position, 4-wire modular jack, compatible with either wall or floor RJ11, RJ12 and RJ13 type jacks.

The CSD-5300 unit is prepared for connection to RJ11 type telephone jacks. If connection to RJ12 or RJ13 type jacks is desired, a jumper must be added on the 5300MB Modem Board module.

The jumper is positioned between relay K2 and transistor Q3 and adjacent to the edge connector pins of the 5300MB module.

## **IMPORTANT:**

- 1. Never install telephone wiring during a lightning storm.

- 2. Never install telephone jacks in wet locations unless the jack is specifically designed for wet locations.

- **3.** Never touch uninsulated telephone wires or terminals unless telephone line has been disconnected at the network interface.

- 4. Use caution when installing or modifying telephone lines.

## **Impulse Drive Output (3-position barrier strip)**

Up to 25 impulse clocks may be connected to the impulse drive connector.

## **Time Code Output**

The SMPTE/EBU Time Code output is available from either of two 3-position terminal blocks. The upper of the two connectors is a low impedance balanced output, capable of +10 dBm unloaded, dropping 3 dB into 180 Ohms. The lower connector is a 600 Ohm balanced output at +4 dBm nominal.

Since clocks such as the LEITCH DAC-5000 Series Digital Analog Clocks bridge high impedance inputs, a large number of clocks may be connected in parallel to this output. However, for purposes of fault isolation, it is recommended that some form of distribution, such as that provided by the LEITCH ADA-800 Series Audio Distribution Amplifiers, be used when connecting more than 20 clocks to the system.

## **Auxiliary Output**

The CSD-5300 unit uses a female 37-pin D connector on the rear panel for auxiliary outputs and external strobe input. The connector is wired as follows:

#### Pin

- 1 Ground

- 2 Time valid (active high)

- 3 1 Hz

- 4 60 Hz/50 Hz

- 5 Serial time clock

- 6 Frame Bit 1

- 7 Frame Bit 3

- 8 Frame Bit 5

- 9 Seconds Bit 1

- 10 Seconds Bit 3

- 11 Seconds Bit 5

- 12 Minutes Bit 0

- 13 Minutes Bit 2

- 14 Minutes Bit 4

- 15 Minutes Bit 6

- 16 Hours Bit 1

- 17 Hours Bit 3

- 18 Hours Bit 5

- 19 100 kHz/1MHz

- 20 External Strobe input (active low)

All outputs from the auxiliary output connector are 5 Volt logic level signals.

The signals on pins 6 to 18 and 24 to 36 give the time in parallel BCD format. The output consists of frame count, seconds, minutes and hours. This output changes 30 times a second to reflect the new frame count. The time information output refers to the present frame, and is updated approximately 100ms before the start of each new frame. As an example, 100 $\mu$ s before noon the output will change from 11 59 59 29 to 12 00 00 00.

Three output signals are used to give the time in serial format. The Serial Time Data output on pin 23 contains the time information which is sent out 30 times a second. The data is sent in the same order as in the time code output, i.e. frame count, seconds, minutes and hours, with the LSB sent first. As in the time code output, the time data refers to the upcoming frame. The Serial Time Clock output on pin 5 goes high at the start of each data bit, and falls 208  $\mu$ s

## Pin

- 21 Tone present

- 22 Impulse clocks stopped

- 23 Serial time data

- 24 Frame Bit 0

- 25 Frame Bit 2

- Frame Bit 4

- 27 Seconds Bit 0

- 28 Seconds Bit 2

- 29 Seconds Bit 4

- 30 Seconds Bit 6

- 31 Minutes Bit 1

- 32 Minutes Bit 3

- 33 Minutes Bit 5

- 34 Hours Bit 0

- 35 Hours Bit 2

- 36 Hours Bit 4

- 37 Serial Time Latch

later. Data should be taken as valid on the falling edge of clock. The Serial Time Latch signal, on pin 37, pulses low approximately 100 ms before the end of each frame. This signal can be used by external circuitry to latch in the serial time data.

As an example, two frames before noon, the serial data output will be 11 59 59 29. During the frame immediately before noon, the serial data output will be 12 00 00 00.

The 1 Hz and 60 Hz/50 Hz outputs on pins 3 and 4 respectively are square waves. These signals are synchronous with the time output of the unit. At the top of each second, both outputs fall. Therefore, these outputs can be used to latch the correct time edge.

The 100 kHz/1 MHz output, on pin 19, is derived from the time base of the unit, but is independent of the time output. The output frequency on this pin is selected by the 100 kHz/1 MHz jumper on the 5300MO module.

The Time Valid output is high when the unit has valid time information. The Impulse Clocks Stopped output is high when the unit has stopped the impulse drive output. The Tone Present output goes high for the duration of any hour or half-hour marker tone output.

When a new time is being input, a 5 Volt logic-level falling edge input or a contact closure on the External Strobe line will synchronize the unit to the external time source. Only the first edge is taken for each separate time input operation. In other words, the unit will not continually accept synchronizing information from a pulse train. Refer to the Operation section of this manual for further information on the use of the External Strobe input.

To lessen the radiation of radio frequency energy and ensure compliance with Part 15 of the FCC rules, it is recommended that a shielded cable such as Belden 9519 be used for connections to the auxiliary output connector.

## **RS232** Connector

The RS232 interface uses a 25-pin female D connector on the rear panel of the CSD-5300 unit. Two communication ports are provided via this connector. One is for the standard terminal interface while the second accommodates the optional 5300RI Reference Interface module. Both ports may be connected at the same time, but only one will operate at a time. The 5300RI has priority.

The connector is wired as follows:

| Pin |                         |

|-----|-------------------------|

| 1   | Protective Ground       |

| 2   | Serial Data In          |

| 3   | Serial Data Out         |

| 4   | Request to Send In      |

| 5   | Clear to Send Out       |

| 6   | Data Set Ready Out      |

| 7   | Signal Ground           |

| 8   | Data Carrier Detect Out |

| 12  | Carrier Detect          |

| 13  | Clear to Send           |

| 14  | Transmit Data           |

| 16  | Receive Data            |

| 18  | Data Set Ready          |

| 19  | Request to Send         |

| 20  | Data Terminal Ready     |

| 22  | Ring Detect             |

| 23  | Speed                   |

|     |                         |

#### Marker Beep Output

The time marker beep output is available from a 3-position terminal block. The output is 600 Ohms balanced at +4 dBm nominal.

The marker beeps are enabled by the DIP switches located at the front of the 5300ET module.

#### **External Reference Input**

The external reference input loop bridges 75 Ohms. The input level must be 2 Vp-p 3 dB. The choice of 5 MHz or 10 MHz as the external reference is made by the 5 MHz/10 MHz jumper on the 5300MO module.

## **Reference Output**

The reference output is 5 MHz at 2 Vp-p into 75 Ohms.

## 1.3.8 Calibration

The only part of the CSD-5300 unit requiring calibration is the 5300MO Master Oscillator module. Please refer to the 5300MO circuit description of this manual for further details.

## **1.4 Operation**

The CSD-5300 Master Clock System Driver can be controlled from either the front panel, an RS232 interface or over the telephone line.

## **1.4.1 Front Panel Control**

The front panel constitutes the simplest and most readily available operational control.

The outside portion of the front panel contains the 6-digit time display, the external reference LED and the impulse clock correction mode LED. The 6-digit time display is duplicated in the inside portion of the front panel, which also contains 11 control mode push buttons, each identified by a number, a plus and a minus selection LED and operation instructions.

To select any of the control modes, press the shift button at the same time as the control mode button. The outside display will then go off while the inside display will show the number corresponding to the control mode that has been selected and a cursor. The number ensures correct selection of the mode while the cursor indicates that the system is ready to accept new information. A 30 second period is available to enter new information. If during this period no information has been entered, the CSD-5300 unit will cancel the control mode and will revert to its original status. After selecting the new information, press <SHIFT/ENTER>, i.e. press the shift button at the same time as the enter key to enter the information and to end the control mode.

If an error is made when selecting new information, the error can be deleted by pressing <SHIFT/CANCEL>, i.e. pressing the shift and cancel buttons simultaneously. This will cancel the control mode also but it will not affect any information previously contained in the unit.

On power-up, the two front panel displays and the impulse clock correction mode LED will flash. This indicates that no time information has been provided to the CSD-5300 unit. Upon entering the time, the flashing will stop.

The control modes operate as follows:

## **Input Time**

The Input Time button is the first control mode of the inside panel. It is used to manually set the time of the unit. Upon selecting this mode, a cursor and the number 2 (corresponding to this mode) should appear in the inside display. The time is then entered in hours, minutes and seconds by pressing the buttons corresponding to the desired numbers.

Two options for synchronizing the CSD-5300 unit to the new time are available:

- 1. The first option consists in simply pressing <SHIFT/ ENTER> after the new time has been selected. The unit will start operating with the time provided at the instant the enter button is pressed.

- 2. The second option is provided for customer applications. It uses the external strobe input from pin 20 of the Auxiliary Output Connector located at the back of the CSD-5300 unit. The strobe input detects an external contact closure (active low). When said closure occurs, the clock will switch to the time provided.

## **Input Date**

The next control mode is the Input Date mode. The date is selected as year, month and day in the same manner as for the Input Time mode.

This mode also allows inspection of the date contained in the CSD-5300 unit prior to selecting a new date. Approximately 3 seconds after selecting this mode, the cursor and the number 3 will go off, and the date contained in the unit will be shown on the inside display. If the existing date is adequate, press <SHIFT/CANCEL> to end the mode without changing the date.

## **Input Impulse Clock Reading**

The Input Impulse Clock Reading mode is the next control mode of the inside panel. This mode is used to eliminate any discrepancy between the readings of the CSD-5300 unit and the impulse clocks connected to it. Upon selecting this mode, the impulse clocks are stopped. The time reading of the impulse clocks is then selected and entered in the same manner as for the Input Time mode. If there is a discrepancy between the readings, the impulse clock correction mode LED of the front panel will light steadily. This will indicate that the unit is acting to correct the discrepancy. The correction mode is carried out by either operating the impulse clocks at twice their normal speed or by stopping them until the time discrepancy is eliminated, whichever is faster. Once the time discrepancy is eliminated, the LED will go off and the clock drive will return to its normal speed.

In the case that no impulse clocks are connected to the clock driver, the impulse clock correction mode LED can be disabled by means of the DIP switch S7 located at the front of the 5300ET module. Switch S7 also stops any impulse clock connected to the unit.

## **Time Offsets**

The next four control modes are time offsets. The first button is used for two offset modes, i.e. the hours, minutes and seconds offset and the auxiliary offset. To select either offset, DIP switch 1 located at the front of the 5300ET module should be set accordingly. To select the HMS mode, ensure that DIP switch 1 is its UP position.

This mode is basically used for leap seconds and for the spring and fall daylight saving/standard time change. Upon selecting this mode and before entering the time offset, selection of the plus or minus control should be made. This is done by pressing the shift button at the same time as the plus/minus button until the desired selection is made. The selection is then entered by pressing <SHIFT/ENTER>. Afterwards, the time offset is selected in the same manner as for the Input Time. The maximum offset allowed is 23 hours, 59 minutes, and 59 seconds.

Two options are available for implementing this offset. The change can be carried out immediately or it can be programmed to occur at any given time, e.g. at 3 AM when most time changes take place to avoid disruptions. To implement the change immediately, press <SHIFT/ENTER> and the offset will be carried out instantaneously. If a delay is desired, select the delay in hours, minutes and seconds and press <SHIFT/ENTER> and the offset will occur at the time selected.

The next control mode, that is the auxiliary offset, is used in applications where it is desired to show the time of a given time zone on one set of clocks and that of its time reference on another set of clocks. The auxiliary offset requires the use of clocks such as the LEITCH DAC-5000 Series which accept Time Code which has a user programmed constant offset inserted as user bits in the time code. Please refer to the Configuration of the Time and Control Code section of this manual for further details.

To select this mode, DIP switch 1 located at the front of the 5300ET module should be in the DOWN position. The mode is then selected in the same manner as the HMS offset with the exception that the auxiliary offset is done in 30-minute increments and the maximum offset allowed is 12 hours. The offset is implemented immediately.

The next control mode is the millisecond offset. This mode allows the clock to change instantaneously from 0 to 999 ms and is selected in the same manner as the hours, minutes and seconds offset. The change, however, is implemented immediately. This offset is basically used to synchronize the CSD-5300 unit to the beep tones of an external time transmission. If, for instance, the unit has an offset of half a second, diminishing offsets can be selected until it becomes synchronized with the time signal.

The fourth control mode provides an offset for the telephone line. This offset is basically used when the CSD-5300 unit is located in a Time Zone other than that of the Reference Standard from which the unit is updating its time via the telephone. If the time difference between the two locations is known, the unit can be programmed to subtract/add this time difference from the time received, so that the clock will maintain local time accurate to the Reference Standard Time.

Upon selecting this mode and before entering the offset, selection of plus or minus should be done and then the <SHIFT/ENTER> buttons pressed. Afterwards select the offset in hours, minutes and seconds and press <SHIFT/ENTER>. Then select the milliseconds offset and again press <SHIFT/ENTER> to end the control mode.

The CSD-5300 unit is also capable of automatically measuring loop-back delay and compensating for propagation delays through telephone lines and satellite telephone links. In cases where the propagation delay is known, it can be provided to the unit by entering a millisecond value to the Input Phone Offset mode and thus the correction will be done manually. It should be pointed out that when any value other than zero is entered, the automatic measuring of the loop-back delay and compensation capability of the unit will be disabled.

## Phone Now

The last control mode of the inside panel is the Phone Now button. This control is used for setting up the CSD-5300N unit for the first time or to verify the accuracy of the display.

Upon selecting this mode and pressing <SHIFT/ENTER>, the unit will initiate an internal test diagnostics. If the test diagnostics is successfully completed, the unit will automatically dial the telephone number of the external standard. For details on how to input a telephone number, please refer to the Input New Telephone Number section of this manual. Once the external standard has been accessed, the time obtained and the unit reset itself, the new time will be immediately shown on the front display.

If, for whatever reason, the call is not successfully completed, the two front panel displays will flash to indicate that a new call is required. This will also create a P code in the Send Status function of the user mode. For further details, please refer to the User Mode section of this manual.

Whenever the Phone Now mode is selected, the call day counter for the automatic phone calls (please refer to the Input New Telephone Number section of this manual) will be reset.

## 1.4.2 RS232 and Telephone Line Control

The CSD-5300 Master Clock System Driver can also be controlled from either the telephone line or an RS232 interface. The RS232 interface may also be used to allow a computer to get time data from the unit. The unit is configured as a data set that plugs directly into video terminals at 300 baud, no parity, one stop bit. The telephone line capabilities are identical to the RS232 protocols with slight exceptions which will be described later.

The video terminal is normally connected locally for diagnostic use, time setting and setting up the characteristics of the unit. The telephone line, on the other hand, is basically used by third parties to obtain the time.

Two basic modes of RS232 and telephone line access are available. These are the user mode and the system mode.

#### 1. User Mode

Whenever the RS232 interface is connected, the CSD-5300 unit is automatically in the user mode. This mode allows access to five basic functions. It also includes a HELP menu which details the commands for the five basic functions. The menu is accessed by typing HELP and then pressing the carriage return. The following will appear on the screen:

| Т  | (CR) | <b>»</b> | SEND | TIME   |

|----|------|----------|------|--------|

| D  | (CR) | *        | SEND | DATE   |

| L  | (CR) | »        | LOOP | BACK   |

| HU | (CR) | <b>»</b> | HANG | UP     |

| S  | (CR) | *        | SEND | STATUS |

The first function provides the time, the second provides the date, the third allows calculations of path delay if an external system is being called, the fourth disconnects the telephone line and the fifth provides the status of the unit. The five basic functions are accessed as follows:

Send Time function; type  $\mathbf{T}$ , press carriage return and the time is sent to the terminal. Refer to the diagram below for the time sequence. The diagram shows the time request from the external device and the response of the CSD-5300 unit. Second boundaries are shown as /.

The time information is sent starting with a carriage return, timed so that the stop bit ends at the start of the next second. This is sent at the end of the second in which the time was requested. The time information is sent for three consecutive seconds in the following format. At the start of the second, the time of the next second is sent as HHMMSS. At the end of the second a carriage return is sent, timed as described above. This allows the carriage

return to function as a cue for the time information. After sending the time, the unit returns to user mode.

/Time Request CR/ HHMMSS CR/ HHMMSS CR/ HHMMSS CR/

## **Time Request Diagram**

- Send Date function: type D, press carriage return and the date is sent once to the terminal. The date is sent in the format YYMMDD and is followed by a carriage return. After sending the date, the unit returns to user mode.

- Loop Back function: type L, press carriage return and the CSD-5300 unit echoes any character sent to it and then returns to user mode. The loop delay can be calculated since the character that was sent would return after twice the path delay.

- **Hang Up function**: in the case the unit is connected to the telephone line, type **HU** and press carriage return and the unit will hang up the telephone.

- Send Status function: type s, press carriage return and the status will be sent to the terminal. There are four different codes to indicate the status of the CSD-5300 unit. G indicates that the unit is operating properly, D that the internal test diagnostics have failed, T that the unit has not been provided with the time and P that the last phone update failed.

The user mode has a 30 second time out when accessed via the telephone line. If after 30 seconds no valid commands have been entered, the CSD-5300 unit sends the time three times and then hangs up. In addition to protecting the unit from outside sources attempting to break in, the 30 second time out allows units with different levels of complexity to take advantage of this service. For instance, a computer with a basic modem which is not capable of using the full protocol can wait for the time out period and then receive the time. Other systems with a greater level of complexity can use the commands, calculate the loop delay and get the time with much greater accuracy.

## 2. System Mode

The second basic mode of RS232 and telephone line access is known as the system mode. This mode allows access to the time setting capabilities of the CSD-5300 unit and will duplicate all of the functions of the front panel. In order to protect the unit against unwanted calls accessing and/or modifying the information contained in the unit, a password is required for RS232 access of the system mode. For telephone access, in addition to the password, the DIP switch S3 located at the front of the 5300ET module has to be enabled. The password consists of two parts. The first part is the word LEITCH. The second part is the serial number of the unit. The serial number of the unit consists of the year that the unit was manufactured plus a four digit number which is the individual number of the unit. This has the advantage that the password can be easily read from the front panel. Another advantage is that LEITCH Video, at

the request of the owner, is able to program the unit and run the test diagnostics program via the telephone. The owner can disable access to the unit by turning off the system access enable switch S3 of the 5300ET module.

To access the system mode, type LEITCH, press carriage return, type the serial number of the unit and press carriage return again. As with most computer systems the password is not echoed on the screen. A system mode prompt with the following message will appear on the display:

```

type HELP (CR) for menu

```

The following is the first question that appears:

do you want line feeds, yes, no?

This is provided for both intelligent and semi-intelligent video terminals and systems, some of which insert their own line feeds. For a basic system that inserts no line feeds, the answer is "yes".

Typing **help** and pressing carriage return will bring up the command menu. There are seventeen functions in the command menu. Each command is identified by a code on the left hand side of the screen, followed by a carriage return (CR) when required and a description of the command.

| M2     | (CR) | * | INPUT NEW TIME               |

|--------|------|---|------------------------------|

| МЗ     | (CR) | » | INPUT NEW DATE               |

| M4     | (CR) | » | IMPULSE CLOCK TIME           |

| M5     | (CR) | * | HOURS, MIN., SEC. OFFSET     |

| Мб     | (CR) | » | MILLI SEC. OFFSET            |

| M7     | (CR) | * | TELEPHONE (HMS & MILLI SEC.) |

| AUX    | (CR) | » | AUXILIARY OFFSET             |

| PHONE# | (CR) | » | INPUT NEW PHONE NUMBER       |

|        |      |   |                              |

| HELP   | (CR) | » | GIVES THIS MENU              |

| TEST   | (CR) | » | SELF DIAGNOSTICS             |

| QUIT   | (CR) | » | BACK TO USER MODE            |

| HANGUP | (CR) | » | HANG UP TELEPHONE LINE       |

| LF     | (CR) | » | LINE FEEDS (Y/N)             |

|        |      |   |                              |

| P      |      |   | PLUS                         |

| М      |      |   | MINUS                        |

| С      |      |   | CANCEL                       |

| (CR)   |      |   | ENTER                        |

The following will appear on the screen:

The first six of the functions are identical to those of the front panel and operate in a very similar manner. To select any of the functions, first type its corresponding code and then, where indicated, press carriage return. Selection of the different functions is as follows:

#### **Input Time**

The Input Time function is the first available command of the help menu. To select this function type **M2** and press carriage return. A prompt will appear on the screen that reads:

ENTER NEW TIME HH MM SS

The time is then typed in hours, minutes and seconds and the carriage return pressed afterwards. If a typing error is made, press c (Cancel) and the error will be eliminated. However, to re-enter the time, the Input Time function has to be selected again.

As in the case of the front panel, two options for synchronizing the unit to the new time are available.

- 1. The first option consists in simply pressing the carriage return after the new time has been typed. The unit will start operating with the time provided at the instant the enter button is pressed.

- 2. The second option uses the external strobe input of the Auxiliary Output Connector to switch to the time provided in the same manner as described for the front panel.

## **Input Date**

The next function is the Input Date command. To select this function type **M3** and press carriage return. A prompt will appear on the screen that reads:

| CURRENT DATE   | ->(date contained in the unit) |

|----------------|--------------------------------|

| ENTER NEW DATE | ->YY MM DD or CR               |

If the current date contained by the unit is acceptable, press carriage return and the message EXIT DATE MODE will appear on the screen. This indicates that the unit is back to system mode, and that the date has not been changed. If it is desired to alter the current date, type the new date as year, month and day and press carriage return. Again, a message showing the new date and the EXIT DATE MODE will appear on the screen to indicate that the change has been recorded and that the unit is back in system mode.

#### **Input Impulse Clock Reading**

The Input Impulse Clock Reading function is the next command of the menu. To select this function type M4 and press carriage return. A prompt will appear on the screen that reads:

ENTER TIME ON IMPULSE CLOCKS

As in the case of the front panel, the impulse clocks connected to the unit will stop upon selecting this function. The time reading of the impulse clocks is then typed and the carriage return pressed in the same manner as for the Input Time function. If there is a discrepancy between the readings, then the impulse clock correction mode LED of the front panel will light steadily to indicate that the unit is acting to correct this discrepancy. As for the front panel, the correction mode is carried out by either operating the impulse clocks at twice their normal speed or by stopping them until the time discrepancy is eliminated, whichever is faster. Once the time discrepancy is eliminated, the LED will go off and the clock drive will return to its normal speed.

#### **Time Offsets**

The next four functions are time offsets and they operate as described for the front panel.

The first function is the hours, minutes and seconds offset. It is selected by typing **M5** and then pressing the carriage return. The following prompt will appear on the screen:

```

ENTER HMS OFFSET & TO OCCUR

M/P & HH MM SS AT HH MM SS

```

First, selection of plus or minus is made. Type either P or M, as desired, and press carriage return. Then select the offset in hours, minutes, and seconds and press carriage return. The maximum offset allowed is 23 hours, 59 minutes, and 59 seconds as for the front panel.

Two options are available for implementing the offset. The change can be carried out immediately or it can be programmed to occur at any desired time.

To implement the change immediately, press the carriage return and the offset will be carried out instantaneously.

If it is desired to program the change at a given time, type the time in hours, minutes and seconds and then press the carriage return. The offset will occur at the time selected.

The next function is the millisecond offset. To select this function type **M6** and press carriage return. The following prompt will appear on the screen:

ENTER MILLI SEC OFFSET

Selection of plus or minus is made by again typing P or M, as desired, pressing the carriage return and then typing the desired offset (max. 999 ms) and pressing carriage return.

The third function provides an offset for the telephone line. To select it, type M7 and press carriage return. The following prompt will appear on the screen:

ENTER PHONE OFFSETS M/P & HH MM SS

& MMM

Again selection of plus or minus, hours, minutes, seconds, and milliseconds is made as previously described.

The next function is the auxiliary offset. It is selected by typing AUX and pressing carriage return. The following message will appear:

ENTER AUX OFFSET (IN 30 MIN STEPS) M/P & HH MM

Selection of plus or minus and then the offset in 30-minutes increments and up to 12 hours is made as previously described.

#### **Input New Telephone Number**

The next function is the Input A New Phone Number. The objective of this function is to allow several units to be arranged in a hierarchical system; i.e. a reference unit connected to a Cesium standard which can provide a standard time to several local units.

To select this function type **PHONE#** and press carriage return. A prompt will appear on the screen that reads:

CALL DAY » XX

This message requests the desired frequency of calls to the reference unit in number of days. If the existing number of days is adequate, press carriage return. If it is desired to modify it, select the new number, press carriage return and the change will be recorded. Obviously, if zero is selected as the number of days, the unit will never call the reference unit.

After the call day has been entered, the following prompt will appear on the screen:

CALL TIME -> XX XX XX

This message requests the time of the day in which the call is to be made. If the existing time of the day is adequate, press carriage return. If it is desired to modify it, select the new time in hours, minutes and seconds, press carriage return and the change will be recorded. Normally this can be set for the middle of the night when telephone trunks are more readily available and calls are cheaper. If there is no answer, e.g. the trunk is not available or the unit to which the call is being made is busy, it will hang up and wait a random period of time before recalling. A total of seven attempts will be made to contact the unit. If after the seventh attempt no contact has been made, the unit will indicate that the telephone update has failed by sending a P code to the Send Status function of the user mode. It will also reset the call day counter and therefore will wait the existing number of days before recalling again.

In the case of a power failure, the unit, after waiting for a period of 20 minutes to allow the crystal oscillator oven to warm, will phone automatically and reset the call day counter if the call day recorded is not equal to 00 days.

After the call time has been recorded, the following prompt will appear on the screen:

PHONE # -> XXXXX

This message requests for a telephone number. If the existing number is acceptable, press carriage return and the number will be kept. If a new telephone number is desired, type the new number and press carriage return. The unit will accommodate both dial pulse and DTMF as well as the delay required for a PBX to obtain an outside line. Three different codes are available to indicate the type of dial and the delay. These are P for pulse, T for touch tone and D for delay. To enter a new phone number, first indicate the type of dial, P or T. After, for instance, entering a P it will remain in pulse mode until a T is entered.

As an example, enter P1 T416 4459640. This would have the effect of pulsing a 1 and then dialing in DTMF the area code and the remaining seven numbers. If a PBX is available and, for example, it is desired to access an old model that accepts pulse only, P9 can be entered which will give pulse 9 for an outside line, then D3 which will provide a delay of 3 seconds for obtaining an outside line and then T followed by the number to call.

The phone number input routines will accept spaces and dashes. These can be entered to format the output so that the phone number is easily readable on the screen. The total number of characters of a phone number input routine, including T, P, and D, is twenty five.

#### System Mode Menu

The next command is the System Mode Menu function. When typing **HELP** and pressing carriage return, the system mode menu will appear on the screen.

## **Self Diagnostics**

The next command of the system mode menu is the self diagnostics function. When typing TEST and pressing carriage return, the unit will enter a diagnostics cycle. The diagnostics cycle is the same to that performed when the unit calls an external source or on power up. The following will appear on the screen:

EEPROM TEST-> PASSED (or FAILED) RAM TEST -> PASSED (or FAILED) PGM TEST -> PASSED (or FAILED) MODEM TEST -> PASSED (or FAILED) DIAGNOSTICS DONE.....

In the case the test diagnostics fail, please contact LEITCH's Service Department.

## **Back To User Mode**

The Back To User Mode function is the next command of the system mode menu. When typing QUIT and pressing carriage return, the unit will return to the user mode.

#### Hang Up the Telephone

The next command of the menu is the Hang Up The Telephone Line function. When typing HANGUP and pressing the carriage return, the unit will hang up the telephone and will return to the user mode.

#### Line Feeds

The next command of the system mode menu is the Line Feeds function. When typing **LF** and pressing carriage return, the following message will appear on the screen:

DO YOU WANT LINE FEEDS?  $(Y/N) \gg Y$  or (N)

This command will alter the information provided when first accessing the system mode.

#### **Miscellaneous Commands**

Four other commands are available in the system mode menu. These are

- C for cancel,

- CR for enter,

- P for plus, and

- M for minus.

When selecting any of these commands, it is not required to press carriage return. The commands are self-explanatory; therefore no further details are provided.

#### Set Window

The Set Window function is not included in the system mode menu due to the fact that if these values are assigned incorrectly, all outgoing telephone calls would fail. All units are pre-programmed with the default prior to delivery.

The purpose of this function is to attempt to detect asymmetrical path delays when an external system is being called i.e. a call being placed via satellite in one way and via land line on the other. All calls received with a delay that falls within the values set by the window will automatically be rejected.

To access this function, type **SET** and press carriage return. The prompt WHAT? will appear on the screen. The purpose of this message is to protect the unit against unwanted modifications of the default. Then type **WINDOW** and again press carriage return and the following will appear on the screen:

Select the lower value of the window and then press the carriage return. If the existing value is adequate simply press carriage return and the value will be maintained.

Then, the following prompt will appear on the screen:

ENTER UPPER VALUE IN XXXX MILLI SEC.

**»**

The upper value of the window is then selected as previously described for the lower window, and the following will appear on the screen:

ILLEGAL DELAY WINDOW IS BETWEEN (new values selected)

EXIT DELAY WINDOW MODE

This message will indicate the new values contained by the unit and that this function is completed.

## Autochange / Normal Mode Selection

DIP switch 8 at the front of the 5300ET module selects either the Autochange Mode when set in the up position or the Normal Mode of operation when set in the down position.

The Autochange Mode is selected in cases such as whenever a Clock Autochange system is used with two CSD-5300 drivers to provide continuity of impulse drives, time code signals, etc. In the case of a malfunction to the assigned Master Driver, the Clock Autochange will switch from one driver to the other. When the Clock Autochange Mode is selected, the success or failure of a telephone call to be carried through will not affect the Time Valid Line.

When the Normal Mode is selected, the success or failure of a telephone call to be carried through will affect the status of the Time Valid Line.

## **1.5 Operation Summary**

## 1.5.1 Front Panel

The front panel constitutes the simplest and most readily available operational control. The following functions are available:

| Input Time    | Press SHIFT/Input Time buttons simultaneously. Select the time in                                                                                                                                                                                                                                                                                                                                              |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|               | HH MM SS. Press <shift enter=""> to instantaneously input new time or strobe pin 20 of the Auxiliary Output Connector to synchronize the new time to an external source.</shift>                                                                                                                                                                                                                               |

| Input Date    | Press SHIFT/Input Date buttons simultaneously. Inspect date of unit. If adequate, press <shift cancel=""> to end function. To alter existing date, select date in YY MM DD and press <shift enter="">.</shift></shift>                                                                                                                                                                                         |

| Input Impulse | Press the SHIFT/Input Impulse Clock Reading buttons simultaneously. Enter the readings of Clock Reading the impulse clocks and press <shift enter="">.</shift>                                                                                                                                                                                                                                                 |

| HMS Offset    | Set DIP switch 1 at front of 5300ET in the UP position. Press the SHIFT/HMS Offset buttons simultaneously. Select P or M and simultaneously press the SHIFT button. Press <shift enter="">. Then select the offset (max. 23 h. 59 m. 59 s). To implement the offset instantaneously, press <shift enter="">. If to occur at a certain time, enter the time and press <shift enter="">.</shift></shift></shift> |

| Auxiliary     | Set DIP switch 1 at front of 5300ET in the DOWN position. Press the SHIFT/AUX Offset buttons simultaneously. Select P or M and simultaneously press the SHIFT button. Press <shift enter="">. Then enter the offset (in 30 minute increments and max. 12 h) and press <shift enter="">.</shift></shift>                                                                                                        |

| Milliseconds  | Press the SHIFT/Millisec Offset buttons simultaneously. Select P or M and simultaneously press the Offset SHIFT button. Press <shift enter="">. Then enter the offset (0 to 999 ms) and press <shift enter="">.</shift></shift>                                                                                                                                                                                |

| Telephone     | Press SHIFT/Telephone Offset buttons simultaneously. Select P or M and<br>simultaneously press the SHIFT Offset button. Then press<br><shift enter="">. Enter offset &amp; press <shift enter="">. Select<br/>millisec offset &amp; press <shift enter=""></shift></shift></shift>                                                                                                                             |

| Phone Now     | Press SHIFT/Phone Now buttons simultaneously, then <shift enter="">. Upon completing the test diagnostics, the unit will automatically dial the telephone number provided. Please refer to System Mode section for details to input phone. To cancel this function, press <shift cancel="">.</shift></shift>                                                                                                   |

## 1.5.2 RS232 And Telephone Line Control

## User Mode

Whenever the RS232/telephone interface is connected, the unit is automatically in User Mode. The following functions are available in this mode:

| Send Time   | Type T and press CR. The time will be provided for three consecutive seconds. |

|-------------|-------------------------------------------------------------------------------|

| Send Date   | Type D and press CR. The date will be provided once.                          |

| Loop Back   | Type L and CR. The next character selected will be echoed.                    |

| Hang Up     | Type HU and CR. The unit will hang up the telephone.                          |

| Send Status | Type S and CR. The status will be sent to the terminal.                       |

## System Mode

To access the System Mode, type LEITCH, press CR, type the serial number of the unit and press CR. The following functions are available:

| Line Feeds                     | Type LF and press CR. The message 'Do you want line feeds' will appear<br>on the screen. Type Y for basic systems and N for systems which insert<br>their own line feeds and then press CR.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Help Menu                      | Type HELP and press CR. The system menu will appear on the screen.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Input Time                     | Type M2 and press CR. The message, Enter New Time -> HH MM SS, will appear. Type the desired new time and press CR to input the time instantaneously or strobe pin 20 of the Auxiliary Output Connector.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Input Date                     | Type M3 and press CR. The message, Current Date -> YY MM DD Enter<br>New Date » YY MM DD or CR, will appear. If the existing date is<br>acceptable, press CR. If desired to change, type the new date and press<br>CR.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Input Impulse<br>Clock Reading | Type M4 and press CR. The message, Enter Impulse Clock Time<br>» HH MM SS Clock Reading, will appear. Select the time and press<br>CR.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| HMS Offset                     | Type M5 and press CR. The message, Enter HMS Offset » M/P & HH MM SS & Time to Occur at HH MM SS, will appear. Select P or M press CR, type the offset (max. 23 hours, 59 min. and 59 sec.), press CR and either press CR to implement the change immediately or select the time when the change is to occur and press CR.                                                                                                                                                                                                                                                                                                                                                                                   |

| Milliseconds                   | Type M6 and press CR. The message, Enter Milli Sec Offset » M/P & MMM Offset, will appear. Select P or M, press CR, type offset (max. 999ms) and press CR.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Phone Offset                   | Type M7 and press CR. The message, Enter Phone Offset » P or M & HH MM SS & MMM, will appear. Select P or M press CR, type offset, press CR, type milliseconds offset and press CR.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Auxiliary                      | Type AUX and press CR. The message, Enter Aux Offset (in 30 min steps) » P or M & HH MM, will appear. Offset Select P or M, press CR. Then select the offset in 30-minute increments (max. 12 hours) and press CR.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Input New<br>Phone Number      | Type PHONE# and press CR. The message, Call Day -> XX, will appear.<br>If the existing Phone number is adequate, press CR. If desired to change<br>it, type the new number and press CR. The message,<br>Call Time » HH MM SS, will then appear. If the existing time is adequate,<br>press carriage return. If desired to modify it, type new time and press CR.<br>Then, the message, Phone # » XXXXXX, will appear. If the existing<br>number is adequate press CR. If desired to change it, type the new<br>number (max. 25 characters) by indicating the type of dial (P for pulse<br>and T for touch tone) and, if required, a delay in seconds (D and up to 9<br>sec.) Spaces and dashes are allowed. |

| Self<br>Diagnostics            | Type TEST and press CR. The unit will perform a diagnostics cycle and the results will appear on the screen.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Back to<br>User Mode           | Type QUIT and press CR. The unit will return to the User Mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Hang Up                        | Type HANGUP and press CR. The unit will immediately hang up the telephone.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

## **1.6** Configuration of the Time and Control Code

#### 1.6.1 SMPTE Serial Time Code

The SMPTE Serial Time Code contains the time of the day in hours, minutes and seconds. Since time code was originally intended as a timing and control code for video tape recording, each second is divided into thirty equal parts that coincide with the picture frames of the associated video signal. Thus, each frame can be identified by a unique and complete code address. The time code output of the CSD-5300 is intended only to convey time-of-day information but a frame count is still included. Note that the time code output of the CSD-5300 is non-drop-frame and real time, not color time, and cannot be locked to a video signal.

#### **Code Format**

Each code address consists of eighty bits, numbered 0 through 79. Each address starts at the clock edge before the first address bit (bit zero) which corresponds to the beginning of Line 5 in Fields I and III, as defined in EIA Standard RS170A.

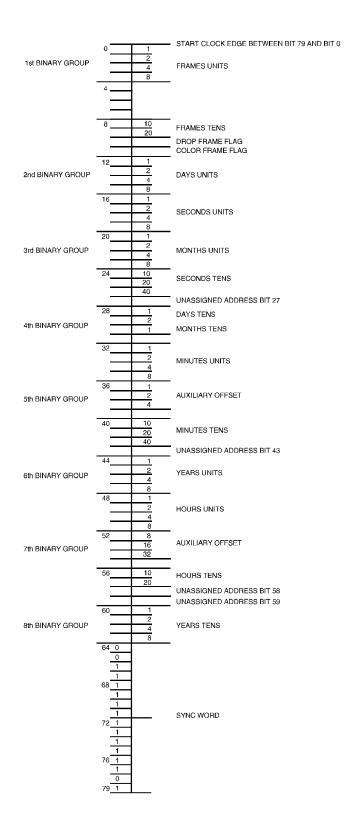

The eighty bits of a code address are assigned as shown in Figure 1-1 on page 1-34 and grouped as follows:

- Eight binary groups consisting of 32 spare user bits.

- Eight time address groups consisting of 28 assigned addresses and four unassigned addresses (all unassigned bits are zeros).

- One synchronizing word consisting of sixteen bits.

The time address groups and the binary groups are arranged alternatively. This is to distinguish the information of a given combination of groups from that of the synchronizing word, which has a typical structure of twelve successive logic ones. If groups of the same type were together, it would be necessary to assign fixed zeros to two of the thirty two bits to prevent an occasional generation of a synchronizing word within the groups. This would reduce the available number of bits to thirty.

The binary groups are intended for storage of user's supplementary data in any fashion and without restrictions.

Figure 1-1: Assigning the eighty bits of a code address

The time address groups use the 24-hour clock system and are based upon the Binary Coded Decimal (BCD) system. Conservation of bits is achieved due to the fact that the count of some addresses does not reach to 9 and, therefore, 4 bits are not always required.

#### **1.6.2** Composition of the Time Address

The eight time address groups (see Fig.1) are arranged as follows:

| Units Frames:  | Bits 0-3; 4 bit BCD arranged 1, 2, 4, 8. Count 0-9.   |